電子機器の高周波化、高速伝送化が進む中で、

誤動作を防止し、安全で安定的な動作を確保するため、

ノイズの対策の重要性が飛躍的に高まっています。

そんなノイズ対策を徹底する上で、

最も重要ともいえることが部品配置の最適化です。

コンデンサ、シールド、抵抗等を設置によるノイズ対策がなされていたとしても、

その部品配置が適切でなければ、思ったような効果を得ることはできません。

当記事では、終端抵抗に焦点を当て、

ノイズを最大限に低減する部品配置に関する技術情報を

シミュレーションを活用した事例を元にお届けします。

- 直列終端抵抗は送信端の近くに配置する

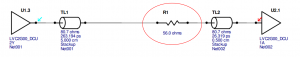

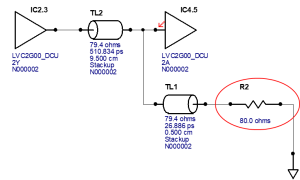

例えば、ノイズの低減を目的とし用いられる56Ωの直列終端抵抗を

下図の通り、送信端から50mm離れた受信端の近くに配置するとします。

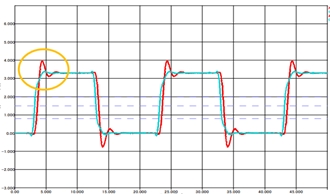

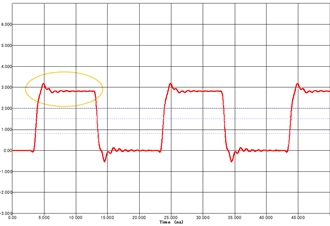

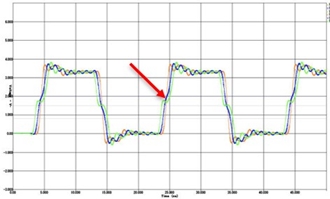

この状態をシミュレーションで解析した結果が下図です。

黄枠で囲っている部分ですが、オーバーシュートが発生しています。

これだけオーバーシュートが発生していると

デバイスの破壊やリンギングによる誤作動につながる恐れがあります。

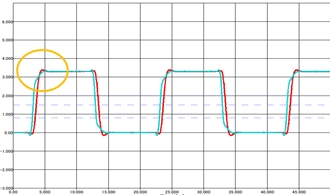

では、反対に、56Ωの直列終端抵抗を

送信端から5mmの位置に配置してみましょう。

この場合のシミュレーション結果が下図となります。

オーバーシュートが解消されていることがお分かり頂けるかと思います。

つまり、ノイズ低減効果を最大限発揮するためには、

直列終端抵抗を送信端の近くに配置することが重要なのです。

下記動画にて詳しく解説しておりますので、

気になった方は是非ご覧ください。

簡単にできるノイズ対策!(シミュレーション編) ノイズ低減効果を最大限にする抵抗の配置

- 並列終端抵抗は受信端の後に配置する

先程の例では直列終端抵抗は送信端の近くに配置するとご説明しました。

しかし、並列終端抵抗の場合は全く異なり、受信端の近くに配置することが重要です。

ただし、とにかく受信端の近くに配置すれば良いというわけではありません。

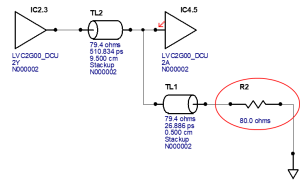

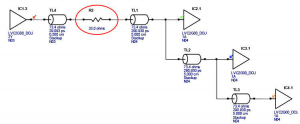

下図では、80Ωの並列終端抵抗を受信端から5mm程度、前に配置しています。

この状態でのシミュレーション結果は下図の通りです。

分かりやすい部分を黄枠で囲っていますが、

少しオーバーシュート・リンギングが発生しています。

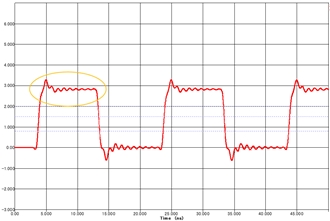

次に、80Ωの並列終端抵抗を受信端より5mm程度、後ろに配置してみます。

この場合のシミュレーション結果は下図の通りです。

受信端より前に配置したときよりパターンが長くなっていますが、

オーバーシュートとリンギングが小さくなっています。

この通り、並列終端抵抗は最終受信端の前ではなく、

後に配置することで、ノイズ低減効果を最大化することが可能です。

下記動画でさらに詳しくご紹介しています。是非ご覧ください。

簡単にできるノイズ対策!(シミュレーション編) ノイズを抑える終端抵抗の配置のポイント

- 複数のICが連なっている場合は、受信端近くに終端抵抗を配置する

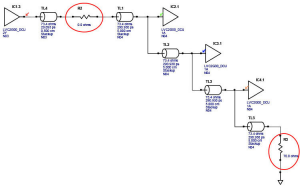

最後は少し複雑な一筆書き配線の例をご紹介します。

複数のICが連なっている回路ですが、

送信端側・受信端側のどちらに終端抵抗を配置するべきなのでしょうか。

まずは下図の通り、送信端側に配置してみます。

(※配置位置を鑑みて、終端抵抗は33Ωとしています。)

シミュレーション結果は下図の通りです。

リンギングが発生しており、反射の影響か、

IC2側のエッジに段付きが見られます。

送信端側のダンピング抵抗は「0Ω」として削除しています。

(※配線インピーダンスは73Ω程なので、終端抵抗は70Ωとしています。)

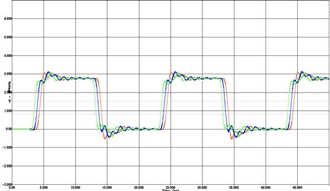

シミュレーション結果は下図の通りです。

前述のシミュレーション結果と比較すると、

エッジの段付きが少し抑えられ、反射が収まっています。

この結果から分かる通り、

複数のICが連なっている場合は、最終受信端近くに終端抵抗を配置することで

ノイズ低減効果を最大化することが可能です。

ただし、パターン設計時にはスペースの関係などで

思うような配置、配線もできないこともありますので、

送信端側、受信端側のどちらかに終端抵抗を追加するか、

状況により検討する必要があります。

下記動画にて当事例を詳しく解説しています。

「もっと詳しく知りたい!」という方は、是非動画をご覧ください。

簡単にできるノイズ対策!(シミュレーション編) プレーン共振解析

いかがでしたでしょうか。

今回は、「ノイズを最大限に低減する部品配置~終端抵抗編~」を

ご紹介しました。

これらの事例のように部品配置を最適化するだけで

ノイズの抑制に大きな効果を発揮します。

実際のパターン設計の際に、当記事を少しでも

思い出していただき、ご活用頂けるととても嬉しいです。

アート電子では、部品配置の最適化を含め、

ノイズ対策を徹底した回路・基板設計を得意としております。

また、お客様からご要望いただければ、

今回の事例でも活用していますシミュレーションを駆使して、

解析結果に基づく基板設計を行うことも可能です。

回路・基板設計に関するお困りごとがございましたら、

是非アート電子にお任せください。

また、当社ではその他の多数の技術情報をWEBサイトにアップしていますので、

ご興味をお持ちの方はぜひご一読頂ければと思います。

プリント基板のアート電子株式会社

〒433-8104 静岡県浜松市中央区東三方町23-5 アートテクノ会館

プリント基板のアート電子株式会社

〒433-8104 静岡県浜松市中央区東三方町23-5 アートテクノ会館