近年、電子機器の小型化・軽量化・高性能化が飛躍的なスピードで進んでいるため、

プリント基板の高速化、低ノイズ化、発熱対策等の高度な要求が高まっています。

こういった要求に対応するためには、高度な基板設計技術に加えて、

基板設計前に発生しうる問題を事前に把握できるシミュレーションの活用が

必要不可欠となっています。

当記事では、そんなシミュレーションの中でも、

ノイズ対策に有効なシミュレーションの1つである

「プレーン共振解析」についての情報をお届けします。

(※下記の動画でも詳しく解説しておりますので、

ご興味をお持ちの方は、是非ご覧ください。)

簡単にできるノイズ対策!(シミュレーション編) プレーン共振解析

プレーン共振解析により、EMI抑制の最適な対策を判別!

プレーン共振解析とは、EMI放射ノイズを増大する要因である

プリント基板のGNDプレーンと電源プレーン間の共振を解析するシミュレーションです。

一般的に、対向する電源とGNDのプレーンがあると、ある周波数帯域で共振が発生します。

その結果、共振点周波数でのEMI放射ノイズの増大へとつながる場合があります。

こういった場合に、プレーンの共振を解析することで、

最適な対策の検討を行うことが可能です。

例えば、解析結果に応じて、

プレーン形状の変更、デカップリングコンデンサ・RCスナバ回路の追加等により、

共振レベルを抑え、共振周波数を高い周波数帯へずらし、EMI放射ノイズを抑制するのです。

では、ここからは実際にプレーン共振解析を行った事例を基に

説明を進めていきます。

プレーン共振解析:デカップリングコンデンサの追加による共振点の変動

当事例ではデカップリングコンデンサを追加することにより、

電源-GNDのプレーン共振解析シミュレーションで共振点がどのように変動するかを確認します。

電源とGNDの対向したプレーンがあるとEMI放射ノイズが高周波で共振します。

テストデータは4層基板で、上から部品面、GND層、電源層、はんだ面にしています。

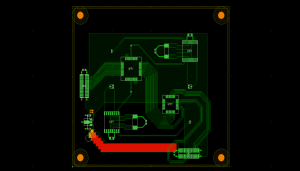

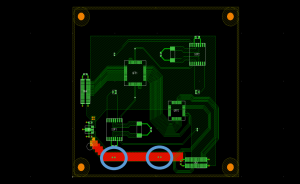

① プレーン上にコンデンサを配置していない場合

下図の赤いラインについて、3層目の電源プレーン、2層目はGNDプレーンです。

プレーンの入り口と出口には0.1uのコンデンサを付けています。

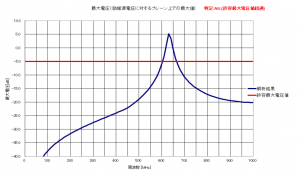

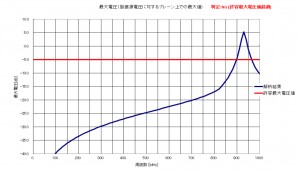

この状態でのシミュレーション結果は下図の通りです。

周波数特性表から共振点が出ています。

結果は周波数特性表から630Mhzあたりでしょうか。

②プレーン上の中央に0.1μmのコンデンサを追加した場合

では、次にこのプレーン上の中央あたりに0.1μmのコンデンサを1つ追加します。

この状態でのシミュレーション結果は下図の通りです。

プレーン上にコンデンサが無い時に比べて、

共振点が高い周波数帯へ少し移動していることが分かります。

800Mhzあたりになりました。

③プレーン上の左側と右側に0.1μmのコンデンサを追加した場合

次はプレーン上の左側と右側に1つずつ、0.1μmのコンデンサを追加してみます。

この状態でのシミュレーション結果は下図の通りです。

コンデンサ1つの時と比べて共振点がさらに高い周波数帯へ少し移動しました。

930Mhzあたりでしょうか。

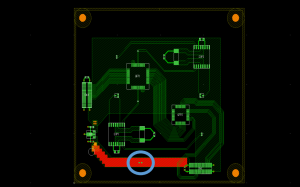

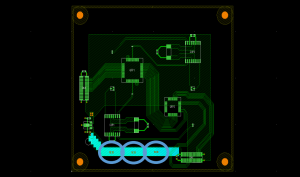

④プレーン上に0.1μmのコンデンサを3つ追加した場合

最後に、下図青丸の位置に0.1μmmのコンデンサを3つ追加します。

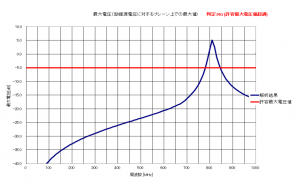

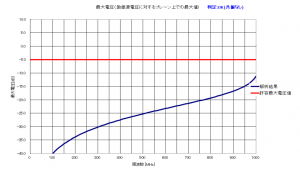

この状態でのシミュレーション結果は下図の通りです。

共振周波数がさらに高い周波数帯へ移動し、

周波数特性表の周波数帯から

無くなっていることがお分かりいただけるかと思います。

いかがでしょうか。

これらの例のようにプレーン共振解析を行うことで

危険な周波数と共振電圧の大きさを確認できます。

そして、解析結果を基に、コンデンサを追加する等の

最適な対策を施すことで共振周波数を高い周波数帯へずらし

共振点が特定の周波数で起こらないようにすることで、

EMIを抑制することが可能となります。

アート電子では、もちろん、このプレーン共振解析をはじめとした

幅広いシミュレーションに対応しております。

お客様のご希望に合わせて最適なシミュレーションを実施し、

高品質な基板設計をサポートいたします。

基板設計・開発に関するお困りごとがございましたら、

是非お気軽にお問い合わせください。

ご相談・お問い合わせはこちら

また、当社ではその他の多数の技術情報をWEBサイトにアップしていますので、

ご興味をお持ちの方はぜひご一読頂ければと思います。

■ プレーン共振解析

■ 用語説明:プレーン共振解析

プリント基板のアート電子株式会社

〒433-8104 静岡県浜松市中央区東三方町23-5 アートテクノ会館

プリント基板のアート電子株式会社

〒433-8104 静岡県浜松市中央区東三方町23-5 アートテクノ会館